ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

19 марта, 2014

19 марта, 2014  Mihail Maikl

Mihail Maikl |

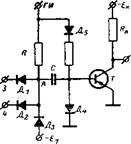

Рис. 38. Динамическая схема запрета с запоминающей емкостью. |

Известно использование конденсатора с разделенными цепями перезарядки в узлах, с помощью которых осуществляется запоминание и хранение информации. Среди таких узлов элемент задержки сигнала на определенное число тактов — основной элемент ряда синхронных цифровых автоматов, а также устройства, в которых информация хранится неограниченное время, а явление саморазрядки конденсатора и разрядки его через вспомогательные цепи компенсируется с помощью регенеративной схемы. Структура этих схем весьма близка к структуре рассмотренных выше схем с конденсаторным дозированием заряда, а приемы анализа многих рабочих процессов аналогичны изложенным выше.

Схема одного из таких устройств, предназначенных для синхронных цифровых автоматов, представлена на рис. 38. Ее наименование— «динамическая схема запрета с запоминающей емкостью» i[Jl. 28]. Часть схемы, содержащая сопротивление R и диоды Ди Дъ, образует логическую схему запрета.

Импульсы напряжения, поступающие от генератора импульсов ГИ, представляют собой симметричное ’(переменно-лолярное) напряжение прямоугольной формы.

При положительных импульсах ГИ и отсутствии сигнала на входах 3 и 4 ток в цепи ЯСД^ заряжает конденсатор С, а при отрицательных импульсах ГИ ток разрядки С, протекая в цепи RC, база — эмиттер, открывает транзистор Т до состояния насыщения и обеспечивает появление на выходе устройства положительного импульса.

Если одновременно с положительным импульсом ГИ на вход 3 подается отрицательный сигнал такой, что точка Л фиксируется на уровне £/«—Uмакс, где UMакс — амплитуда импульсов ГИ, то при очередном отрицательном импульсе ГИ конденсатор не перезаряжается. Прямой ток в эмиттерном переходе Т при этом не появляется, и выходной импульс не возникает.

Таким образом, появление на входе 3 или 4 схемы, изображенной на рис. 38, отрицательного сигнала при положительном импульсе ГИ приводит к исчезновению выходного сигнала, сопутствующего отрицательному импульсу ГИ.

При соединении двух элементов, первый из которых выполнен на транзисторе р-п-р, а второй — на транзисторе п-р-п, или в случае использования трансформаторной связи между элементами появление сигнала «запрет» на входе первого элемента приводит к исчезновению этого сигнала на входе второго и к появлению выходного импульса через период сигнала ГИ. Выходные сигналы первого и второго элементов, соответствующие 1, имеют разную полярность.

Схемы из таких элементов обслуживаются тремя выходами вспомогательного генератора импульсов.

На основе соединения конденсатора с диодами, разделяющими цепи его перезарядки, могут быть разработаны и другие логические элементы для дискретных устройств, питание и синхронизация работы которых осуществляются от единого источника переменного напряжения.

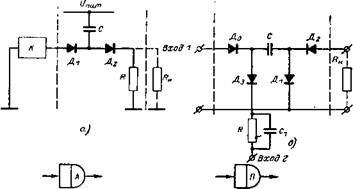

Основные узлы таких элементов — емкостно-диодные элементы задержки, активные (Л. Е. Д. Э. 3.) и пассивные (П. Е. Д. Э. 3.). Эти узлы соответственно представлены на рис. 39,а, б, в, г.

Активный емкостно-диодный элемент задержки образован соединением дозирующего конденсатора С и двух диодов Д и Д2, один из которых Д присоединяется к бесконтактному входному ключу (транзистору или тиристору), а второй Д2 — к нагрузке.

|

|

|

6) г) |

Поясним работу Л. Е. Д. Э. 3., полагая, что его элементы идеальны. При закрытом ключе К дозирующий конденсатор С заряжается до напряжения UMaкс, диод Д2 закрывается, а нагрузочное сопротивление Rn обесточивается.

При подаче на вход ключа К отпирающего сигнала за время соответствующего полупериода напряжения питания конденсатор С перезаряжается ДО —t/макс - В следующий полупериод ДИОД Д2 оказывается открытым, а в RH протекает импульс тока /в ых, сопутствующий перезарядке конденсатора С от —(Умакс ДО +17макс (последнее обеспечивается параметрами Л. Е. Д. Э. 3. Импульс тока переносит в RH дозированный заряд q = 2CUMaKC и при прямоугольном напряжении питания имеет экспоненциальную форму.

Условное обозначение Л. Е. Д. Э. 3. приведено на рис. 39,6.

В пассивный емкостно-диодный элемент задержки (рис. 39,в) входит соединение дозирующего конденсатора С, диодов Д и Д-2, резистора /?, шунтированного конденсатором С, и входных диодов До И Дз-

При подаче на вход 1 П. Е. Д. Э. 3. импульса тока івх конденсатор С заряжается через диоды Д0, Дь а затем, когда входной сигнал уменьшается до определенной величины, закрывается диод До, конденсатор С удерживается в заряженном состоянии. На входе 2, присоединенном к схеме питания, в это время действует положительный потенциал, обеспечивающий запирание диода Д3, а при поступлении в очередной полупериод на вход 2 отрицательного напряжения диод Дз открывается, конденсатор С разряжается по цепи /?нД2Дз (появляется ТОК /вых).

і и

При этом в нагрузку передается заряд inuxdt.

Ток протекает в полупериод, следующий за полупериодом поступления /вх, где /и — время действия импульса.

Емкостно-диодные элементы задержки осуществляют логическую операцию повторения сигнала, представленного токовым импульсом, при этом направление входного тока в цепи, содержащей пассивный элемент задержки, инвертируется. Однако указанная инверсия значения не имеет, так как наличие сигнала, обозначающего, например, единицу, влечет за собой появление сигнала на выходе, а направление тока информации не несет.

Во время формирования выходного сигнала активным и пассивным элементами задержки источник входного сигнала оказывается отключенным (закрыт диод Д на рис. 39,а или Д0 на рис. 39,в).

Пассивный емкостно-диодный элемент задержки может быть представлен условным обозначением по рис. 39,г. Направления входных и выходных токов могут быть заменены противоположными путем изменения направления включения диодов.

Выходной сигнал Е. Д. Э. 3. (токовый импульс) может быть «запрещен» с помощью ключа-транзистора (рис. 40,а), образующего совместно с простейшим фильтром /?фСф схему запрета, управляемую синфазным выходным сигналом. Необходимость фильтра обусловливается инерционными свойствами транзистора. Если элемент запрета устанавливается в П. Е. Д. Э. 3. (после диода Д0), то наличие фильтра становится излишним.

Возможно использование схем, подобных рис. 40,а, для осуществления операции запрета в сочетании с логическими операциями типа ИЛИ и И при наличии на входах определенной группы синхронизированных питанием сигналов. Для этого применяются соответствующие транзисторные и диодно-транзисторные схемы, широко известные из литературы.

Направление включения диодов и тип проводимости транзисторов (р-п-р или п-р-п) в логической схеме, определяющей реализуемую логическую функцию, обусловливают и направление диодов в присоединяемом к такому узлу элементе задержки.

Выходной сигнал Е. Д. Э. 3. может использоваться для питания коллекторной цепи эмиттерного повторителя, осуществляющего передачу сигнала, синхронного с выходным сигналом Е. Д. Э. 3., если последний находится в состоянии 1. Так как процесс зарядки конденсатора заканчивается при токе /с—^0, полупроводниковые приборы, по которым он протекает, характеризуются малотоковым режимом. Это влияет. положительно на работу соответствующих схем, например на схему, состоящую из транзисторной приставки И и активного элемента задержки (см. рис. 40,в).

Из рассматриваемых устройств могут быть построены комплексьї 'синхронных логических элементов, синхронизированных напряжением питания.

Основные цепи таких устройств коммутируются в определенные полупериоды напряжения питания, выходные сигналы синхронизированы напряжением питания, и, наконец, входные сигналы для обеспечения нормальной работы большинства схем па таких элементах

|

|

|

Е. Д. Э. 3. с транзисторным ключом в схеме запрета (а); условное обозначение схемы запрета (б); схема задержанного И (в); функцио- Рис. 40. |

нальная схема задержанного И (г).

должны быть синхронизированы также напряжением питания. Следует отметить, что в А. Е. Д. Э. 3. дозирующий конденсатор может быть заменен диодом и последовательно включенным резистором. При соответствующей полярности напряжения в диффузионной емкости диода может быть накоплен заряд qn=InX. Здесь /п — прямой ток в диоде; т — постоянная времени накопления заряда.

Изменение полярности напряжения питания приводит к появлению в нагрузке импульса /вых, переносящего дозированный заряд qn - Назовем схему транзисторного ключа ИЛИ, содержащего на выходе Л. Е. Д. Э. 3., активным задержанным ИЛИ. Аналогично построена схема активного задержанного И.

Выходной сигнал ни одной из таких схем не может быть использован как входной для аналогичной или другой схемы в связи с отсутствием согласованности. Это обусловливается использованием в них транзисторов с однотипной проводимостью (р-п-р или п-р-п). У таких схем существуют аналоги с иными направлениями входных токов, использующие транзисторы с иной проводимостью.

Выходной сигнал любого из таких устройств — аналогов может быть использован как входной для рассмотренных ранее устройств, а выходной сигнал первых устройств может быть использован как входной для вторых.

|

|

|

б) |

Таким образом, А. Е. Д. Э. 3. вместе с присоединенными к ним логическими приставками оказываются согласованными, если направ

|

|

|

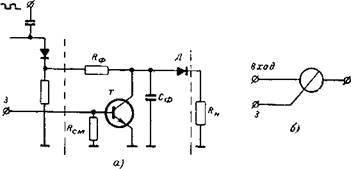

Рис. 41. Схемы линий задержки на активных Е. Д. Э. 3. (а), на активных и пассивных Е. Д. Э. 3. (б) схема динамического триггера (в). |

ления (т. е. полярность) входных токов в них не совпадает (т. е. противоположны).

Здесь под согласованием подразумеваетсяк согласование направления входных и выходных токов.

Последовательное соединение активных задержанных элементов ИЛИ с чередующейся полярностью входных сигналов представляет собой синхронную линию задержки (рис. 41,а). В такой линии иногда представляется целесообразным через один заменить активные задержанные ИЛИ пассивными элементами задержки (рис. 41,6).

Как было указано выше, наличие токового импульса на входе или выходе элемента соответствует единице, а отсутствие импульса — нулю. Единица, поступившая на вход первого элемента линии каждые полпериода питающего напряжения, продвигается на один элемент.

Подобный элемент образует основу схемы динамического триггера, представленной на рис. 41,в.

Очевидно, что рассмотренные выше схемы позволяют строить из них самые разнообразные электронные цифровые устройства, синхронизируемые частотой напряжения питания.

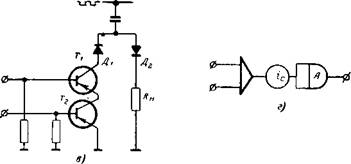

На рис. 42,а представлена схема двухразрядного двоичного реверсивного счетчика, в котором применяются Е. Д. Э. 3. Счетчик питается напряжением, близким к прямоугольному.

|

|

Рис. 42. Схема реверсивного счетчика. а — схема счетчика; б — схема кнопки; в — схема реверсивного разряда.

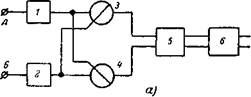

Счетчик содержит кнопки—генераторы одиночного импульса 1 и 2, используемые для ввода асинхронной информации в синхронное устройство (см. рис. 42,6), элементы запрета 3 и 4, предотвращающие счет при поступлении сигналов одновременно на суммирующие и вычитающие входы (Л и Б), и собственно счетные ячейки 5 и 6 (см. рис. 42,в).

На рис. 42,6 показана схема кнопки. Последняя представляет собой синхронную линию задержки из четырех элементов, выход осуществляется со второго элемента через узел «запрет», а на запрещающий вход этого узла подается сигнал с четвертого элемента линии. Элемент задержки в этой линии в отличие от друїих содержит ключ-тиристор (а не ключ-транзистор). Поскольку входным каналом для этого элемента всегда является экспонента (выходной сигнал предыдущего элемента), начало которой синхронизировано с соответствующим фронтом напряжения іпитания, ключ-тиристор Т открывается (если он открывается) только в начале соответствующего полупериода напряжения питания.

|

|

|

|

задержки, если тиристор срабатывает, всегда имеет достаточно большую амплитуду. Этот сигнал запрещает все импульсы, кроме первого в непрерывной серии импульсов на выходе элемента задержки.

На рис. 42,в показана схема одного разряда реверсивного синхронного двоичного счетчика.

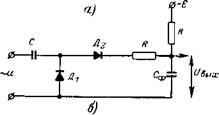

Возвратимся к схеме А. Е. Д. Э. 3., при этом будем полагать, что свободный вывод диода Д2 присоединен к общей шине, а выходные сигналы представлены напряжениями между точками схемы А и Б и общей шиной (рис. 43,а).

Выходной сигнал на выходе Б — постоянное напряжение, причем ^Бвых ^2£/макс соответствует единице, а отсутствие напряжения— нулю. Выходной сигнал на выходе А — пульсирующее напряжение, Причем единице соответствует —£/макс + И(0, а отсутствие напряжения соответствует пулю.

Из-за неидеальности диодов и транзисторных (или тиристорных) ключей напряжение ^Бв.)1Х обычно имеет существенные пульсации, даже при высокоомной нагрузке, которые могут быть уменьшены при подключении конденсатора Сф.

Выходные сигналы, соответствующие единице, присутствуют на выходах, когда нет сигналов на входе, т. е. когда на входе нуль.

Таким образом, для потенциальных сигналов устройство, изображенное па рис. 43,а, является инвертором и осуществляет логическую операцию НЕ. По выходу Б устройство является совместимым. По выходу А устройство является несовместимым с аналогичными, и для его совмещения требуются специальные преобразователи. Однако выход А расширяет логические возможности инвертора — позволяет получить выход по переменному напряжению. Наличие емкости Сф лишь в незначительной степени затягивает переключение, так как при подачи на вход инвертора сигнала 1 емкость Сф разряжается через открытый транзистор, а при появлении на входе нулевого сигнала — заряжается через прямое сопротивление диода и сопротивление источника питания.

Рассеяние мощности в инверторе при статическом режиме несущественно и обусловливается главным образом падением напряжения на прямых сопротивлениях диодов и в выходной цепи.

Наличие переменного напряжения позволяет осуществить инвертор без активного элемента. Схема соответствующего элемента представлена на рис. 43,6. Для нормальной работы схемы необходим вспомогательный источник напряжения Е.

Схема совпадения представлена на рис. 43,в.

Так же как в инверторе, операция над входными переменными реализуется здесь в виде постоянного и переменного напряжений. Сигнал постоянного напряжения формируется дополнительным диодом Ді и емкостью Сф.

Операция ИЛИ может осуществляться с помощью различных схем. Если предыдущий каскад имеет выход по постоянному напряжению, можно воспользоваться обычной диодной схемой, применяемой в цепях постоянного тока. Однако при этом оказывается невозможным строить двухкаскадные пассивные логические схемы, так как рассматриваемая схема не может быть нагружена схемой совпадения и требует применения инвертора на выходе. На рис. 43,г показана схема ИЛИ, свободная от указанного недостатка. Эта схема рассчитана па подключение к выходам переменного напряжения предыдущих каскадов. Благодаря наличию выходного сигнала в виде постоянного напряжения она может быть нагружена любой из описанных выше потенциальных схем. В схеме на рис. 43,г каждый вход имеет отдельный входной выпрямитель, что обеспечивает развязку входных цепей.

Большинство представленных здесь схем — управляемые транзисторами выпрямительные схемы с удвоением напряжения. Поэтому при малых нагрузках величина выпрямленного напряжения на выходе приближается к удвоенному значению напряжения питания.

Скорость переключения таких схем при низких частотах напряжения питания определяется частотой питающего напряжения. Практически можно считать, что максимальная частота переключения в устройствах, соответствующих приведенным схемам, не превышает частоты питания. Приведенные логические схемы некритичны к амплитуде и частоте питающего напряжения и допускают значительные вариации параметров деталей.

При объединении логических схем переменного тока значительное число деталей оказывается лишним. Так, например, если инвертор нагружается только схемой совпадения, из его схемы можно

|

сумматора. |

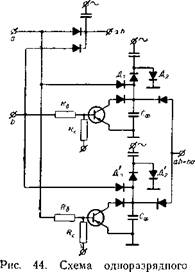

исключить фильтрующую

емкость Сф, а также диодноемкостную цепь, играющую роль коллекторного сопротивления. В тех случаях, когда схема совпадения нагружается по переменному току, из нее могут быть исключены фильтрующий конденсатор Сф и развязывающий диод. На рис. 44 приведена схема одноразрядного сумматора. В этой схеме информация на входах и выходах представлена в одинаковой форме в виде уровней постоянного напряжения. Благодаря этому сочленение таких схем не представляет трудности. Однако следует помнить о необходимости согласования сопротивлений.

Преобразование переменного напряжения в постоянное легко произвести с помощью выпрямителей с накоплением. Обратное преобразование можно произвести с помощью ключа, используемого как модулятор, и управляемого напряжения питания.

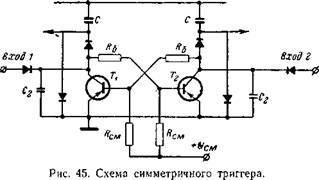

Триггерные схемы, питающиеся переменным током, могут быть

|

|

подобно статическим триггерам построены из двух инверторов. Одна из таких схем показана на рис. 45. Триггер может управляться по раздельным входам и обладает возможностью счетного запуска.

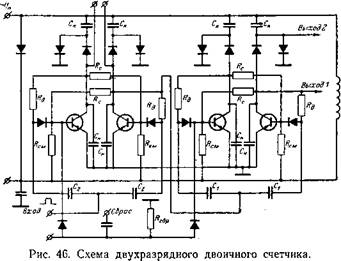

На рис. 46 приведена схема двухразрядного двоичного нереверсивного счетчика, построенного на двухинверторных триггерах переменного тока.

|

|

Параметры элементов схемы триггеров, составляющих этот счетчик: Ск=0,0022 мкф Сн=0,01 мкф; Ci2=0,01 мкф; Rcм = 8,2 ком; /?с = 8,2 ком; /?д = 8,2 ком тоиоды МП16Б; диоды Дд; частота напря-

|

пит

|

жения питания 100—200 кгц; напряжение питания £/Пит = 10 в; максимальная допустимая частота следования входных импульсов 10 кгц.

Мощность, потребляемая каждой триггерной ячейкой, составила менее 20 нет. Значительная часть реактивной мощности, потребляемой счетчиком, компенсируется устанавливаемым на выходе источника питания дросселем.

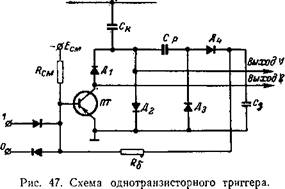

Наличие у инвертора выхода по переменному напряжению позволяет осуществить схемы триггеров с одним транзистором. Одна из таких схем показана на рис. 47. Схема работает следующим образом. В исходном состоянии транзистор инвертора открыт напряжением, Приложенным К нему через сопротивление смещения Rсм-

При этом сигнал в цепи обратной связи отсутствует. Если транзистор запереть внешним сигналом, то на выходе инвертора появится переменное напряжение, а на емкости С3 — 'напряжение положительной полярности. Благодаря этому транзистор будет удерживаться в запертом состоянии. (В приведенной схеме положительная обратная связь имеет запирающий характер.)

Считая напряжение смещения напряжением уставки, последнее устройство можно рассматривать как частотное реле, с другой стороны, при наличии постоянной величины частоты и напряжения питания, полагая напряжение смещения входным*, это же устройство можно рассматривать как реле напряжения — аналоговое устройство с релейной характеристикой.

Логические и спусковые схемы на основе конденсатора с разделенными цепями перезарядки весьма разнообразны и могут осуществлять самые разнообразные функции.

Уменьшенное количество резисторов в схемах, особенно в коллекторных цепях, приводит к резкому уменьшению активных потерь.

Последнее обстоятельство в сочетании с тем, что большинство рассматриваемых узлов не содержит моточных деталей, делает возможным их осуществление в виде микромодульных, гибридных, пленочных и интегральных схем.

Принцип действия рассматриваемых устройств и результаты испытаний отдельных макетов позволяют полагать, что они окажутся некритичны к параметрам отдельных компонентов и к параметрам напряжения питания.

Рассматриваемые устройства могут управляться сигналами устройств постоянного тока и управлять последними.

Наконец, применение переменно-полярного напряжения позволяет осуществлять питание отдельных частей сложных схем от отдельных трансформаторов и в случае необходимости использовать трансформаторы для согласования входов и выходов сочленяемых узлов.

ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С ИСПОЛЬЗОВАНИЕМ ЭКСПОНЕНЦИАЛЬНОЙ ФОРМЫ КРИВОЙ ПЕРЕЗАРЯДКИ

Примером вычислительных устройств такого типа может служить устройство, реализующее соотношение

-*1

y = k In.

Входные сигналы, соответствующие и х2, представлены напряжениями Uі и U2, а выходной сигнал — длительностью выходного импульса Ги.

Принцип действия устройства состоит в следующем. Напряжение U преобразуется в импульс

иі = и1е~ІІ

а затем вырабатывается сигнал, длительность которого t определяется соотношением:

Uxe

Во время работы схемы на входы 1 и 2 поступают соответственно напряжения Ui и IJ2.

На третий вход 3 приходит импульс, который опрокидывает выходной триггер и одновременно отключает вход 1. При этом на емкости Сі и разрядном сопротивлении формируется напряжение вида Ue~^z которое сравнивается с помощью компаратора с напряжением f/г. Когда Ue ^становится равішм U2, на 'выходе компаратора появляется импульс, опрокидывающий триггер в исходное состояние.

Материал предоставлен И. С. Кузнецовым.

В результате на выходе триггера формируется импульс, длительность которого пропорционально логарифму .отношения входных напряжений,

Опубликовано в

Опубликовано в